| |

| ARM CPU configuration |

|

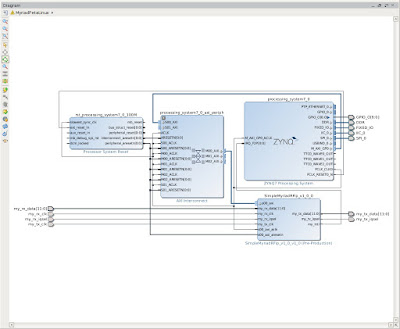

| System block diagram |

|

| Random data being transmitted |

After a lot of studying I have managed to make some progress on my next gen DATV

project. This is all relatively new technology for me so it has taken a lot longer than

I had hoped. Some of the time was wasted by the rather poor documentation of

the sample clock generation chip on the Zipper board but I think I have it correct now.

I have a working PetaLinux installation, GPIO, I2C and SPI control of the devices

on the Zipper and MyriadRF boards.

Interfacing of my custom IP logic in the FPGA to the ARM device uses generic io

and interrupts.

The IP in the PL (FPGA) is currently very simple but will be expanded to provide

many more advanced features. It takes IQ samples from the host and sends them

to the MyriadRF board for transmission. The ultimate aim will be to add Digital

Pre-Distortion code in the PL logic to correct for non linearities in the transmit

chain. On transmit the receive channel will monitor the transmitter output and

carry out the required real time maths. On the receive obviously the receive channel

will be used for demodulation of the received signal.

In the first phase I am simply going to use a PC based program like GNURadio

or DATV-Express to generate samples that will be sent to the Zedboard via

Gigabit Ethernet. I will probably post again when I have something sensible to

transmit.

Hi Charles,

ReplyDeleteProgress! Admire your stamina.

You speak of real-time DPD. Have you considered a fixed DPD implementation based on a characterization of the Tx (dynamic) non-linearities using a typical high PAR signal like DVB-T? I.e. train a the pre-distorter algorithm in SW (e.g. GNU-radio) on IQ data of the distorted known signal captured after the PA and then program this predistorter in FPGA. This would prevent challenges with delays and loop stability and HDL programming in a real-time feedback path. (And free-up the Myriad Rx channel while in Tx to do something else, like duplex ATV.)

See e.g. Lei Ding, Zhou G.T., Morgan D.R., Zhengxiang Ma, Kenney J.S., Jaehyeong

Kim, Giardina C.R., “A robust digital baseband predistorter constructed

using memory polynomials,”

or Ding's PhD thesis on the subject for some more detail.

Anne Westra PE1GTA

Hi Anne,

ReplyDeleteI have done a fair amount of background reading on DPD and I was going to do

something along the lines of the example on the MATLAB site. At the end of the

day I will probably do what is feasible. Rob M0DTS has done some experiments

using DATV-Express and an RTL dongle for basic DPD, he was able to achieve

about a 10 dB improvement but it was very fiddly to set up. I reproduced what he

had done and got similar results.

One advantage I hope of using the Zynq is the close couple between the ARM

device and the FPGA fabric. As well as the ARM9 cores it should also be

possible to use the FPGA fabric as a dedicated maths co-processor.

At the moment I will just be happy to get a basic radio to work. The FPGA

tools are riddled with 'features', stuff that should just work seems to

required multiple Google searches of the Xilinx site to find the correct workaround.

My latest issue is to do with packaging my IP that uses Xilinx IP inside it.

This requires manual intervention, the automatic tool does not seem to work

properly without manual help. Oh the Joy.

- Charles

Hi Charles,

DeleteInterestingly the Matlab DPD example mentioned in your feb 2015 blog is based on same memory polynomial approach as described in Ding's paper.

(D.R. Morgan is author in both referenced papers.)

My suggestion was merely to measure the real PA (stimulate and capture IQ data with Myriad-RF) in non-real-time and with that information train a pre-distorter model until convergence in SW and use results to program the HW pre-distorter model in the FPGA.

Good luck in tying your and Xilinx IP together.

Anne Westra @justatoms